# NVM Express<sup>®</sup> NVMe<sup>®</sup> over PCle<sup>®</sup> Transport Specification

Revision 1.0e July 1st, 2024

Please send comments to info@nvmexpress.org

NVMe® over PCle® Transport Specification, Revision 1.0e is available for download at <a href="https://nvmexpress.org">https://nvmexpress.org</a>. The NVMe® over PCle® Transport Specification, Revision 1.0e incorporates NVMe® over PCle® Transport Specification, Revision 1.0 (refer to the NVMe® over PCle® Transport Specification change list <a href="https://nvmexpress.org/changes-in-nvm-express-revision-2-0">https://nvmexpress.org/changes-in-nvm-express-revision-2-0</a> for details), ECN 001, ECN102, ECN110, ECN111, ECN112 and ECN120.

### SPECIFICATION DISCLAIMER

### **LEGAL NOTICE:**

### © 2008 to 2024 NVM Express, Inc. ALL RIGHTS RESERVED.

This NVMe over PCIe Transport Specification revision 1.0e is proprietary to the NVM Express, Inc. (also referred to as "Company") and/or its successors and assigns.

**NOTICE TO USERS WHO ARE NVM EXPRESS, INC. MEMBERS**: Members of NVM Express, Inc. have the right to use and implement this NVMe over PCIe Transport Specification revision 1.0e subject, however, to the Member's continued compliance with the Company's Intellectual Property Policy and Bylaws and the Member's Participation Agreement.

NOTICE TO NON-MEMBERS OF NVM EXPRESS, INC.: If you are not a Member of NVM Express, Inc. and you have obtained a copy of this document, you only have a right to review this document or make reference to or cite this document. Any such references or citations to this document must acknowledge NVM Express, Inc. copyright ownership of this document. The proper copyright citation or reference is as follows: "© 2008 to 2024 NVM Express, Inc. ALL RIGHTS RESERVED." When making any such citations or references to this document you are not permitted to revise, alter, modify, make any derivatives of, or otherwise amend the referenced portion of this document in any way without the prior express written permission of NVM Express, Inc. Nothing contained in this document shall be deemed as granting you any kind of license to implement or use this document or the specification described therein, or any of its contents, either expressly or impliedly, or to any intellectual property owned or controlled by NVM Express, Inc., including, without limitation, any trademarks of NVM Express, Inc.

### **LEGAL DISCLAIMER:**

THIS DOCUMENT AND THE INFORMATION CONTAINED HEREIN IS PROVIDED ON AN "AS IS" BASIS. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, NVM EXPRESS, INC. (ALONG WITH THE CONTRIBUTORS TO THIS DOCUMENT) HEREBY DISCLAIM ALL REPRESENTATIONS, WARRANTIES AND/OR COVENANTS, EITHER EXPRESS OR IMPLIED, STATUTORY OR AT COMMON LAW, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, VALIDITY, AND/OR NONINFRINGEMENT.

All product names, trademarks, registered trademarks, and/or servicemarks may be claimed as the property of their respective owners.

The NVM Express® design mark is a registered trademark of NVM Express, Inc. PCI-SIG®, PCI Express®, and PCIe® are registered trademarks of PCI-SIG.

NVM Express Workgroup c/o VTM, Inc. 3855 SW 153<sup>rd</sup> Drive Beaverton, OR 97003 USA info@nvmexpress.org

# **Table of Contents**

| 1 In                            | NTRODUCTION                             | 6      |

|---------------------------------|-----------------------------------------|--------|

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | OverviewScopeConventionsDefinitions     | 6<br>6 |

| 2 T                             | RANSPORT OVERVIEW                       | ε      |

| 3 T                             | RANSPORT BINDING                        | g      |

| 3.1<br>3.2                      | Setup & Initialization                  |        |

| 3.3<br>3.4                      | Resets                                  | 11     |

| 3.5<br>3.6                      | Interrupts                              | 13     |

| 3.7<br>3.8                      | Error Handling Model                    | 16     |

| Anne                            | EX A. HOST CONSIDERATIONS (INFORMATIVE) | 36     |

| A.1<br>A.2                      |                                         | 36     |

| A.3                             | · ·                                     |        |

# Table of Figures

| Figure 1: NVMe Family of Specifications                                                              | 6  |

|------------------------------------------------------------------------------------------------------|----|

| Figure 2: Example of Transport Protocol Layers                                                       |    |

| Figure 3: PCI Express Registers                                                                      | 9  |

| Figure 4: PCI Express Specific Controller Property Definitions                                       | 9  |

| Figure 5: Offset (1000h + ((2y) * (4 << CAP.DSTRD))): SQyTDBL – Submission Queue y Tail Doorbell     | 10 |

| Figure 6: Offset (1000h + ((2y + 1) * (4 << CAP.DSTRD))): CQyHDBL – Completion Queue y Head Doorbell |    |

| Figure 7: Create I/O Completion Queue – Command Dword 11                                             |    |

| Figure 8: Command Processing                                                                         |    |

| Figure 9: Pin Based, Single MSI, and Multiple MSI Behavior                                           |    |

| Figure 10: PCI Express Type 0/1 Common Configuration Space                                           |    |

| Figure 12: Offset 04h: CMD - Command                                                                 |    |

| Figure 13: Offset 06h: STS – Device Status                                                           |    |

| Figure 14: Offset 08h: RID - Revision ID                                                             |    |

| Figure 15: Offset 09h: CC - Class Code                                                               |    |

| Figure 16: Offset 0Ch: CLS – Cache Line Size                                                         | 18 |

| Figure 17: Offset 0Dh: MLT – Master Latency Timer                                                    |    |

| Figure 18: Offset 0Eh: HTYPE – Header Type                                                           | 19 |

| Figure 19: Offset 0Fh: BIST – Built-In Self Test (Optional)                                          |    |

| Figure 20: Offset 10h: MLBAR (BAR0) – Memory Register Base Address, lower 32-bits                    |    |

| Figure 21: Offset 14h: MUBAR (BAR1) – Memory Register Base Address, upper 32-bits                    |    |

| Figure 22: Offset 18h: BAR2 - Index/Data Pair Register Base Address or Vendor Specific (Optional)    | 20 |

| Figure 23: Offset 28h: CCPTR – CardBus CIS Pointer                                                   | 20 |

| Figure 24: Offset 2Ch: SS - Subsystem Identifiers                                                    | 21 |

| Figure 25: Offset 30h: EROM – Expansion ROM (Optional)                                               | 21 |

| Figure 26: Offset 34h: CAP – Capabilities Pointer                                                    | 21 |

| Figure 27: Offset 3Ch: INTR - Interrupt Information                                                  |    |

| Figure 28: Offset 3Eh: MGNT – Minimum Grant                                                          |    |

| Figure 29: Offset 3Fh: MLAT – Maximum Latency                                                        |    |

| Figure 30: PCI Power Management Capabilities                                                         |    |

| Figure 31: Offset PMCAP: PID - PCI Power Management Capability ID                                    |    |

| Figure 32: Offset PMCAP + 2h: PC – PCI Power Management Capabilities                                 |    |

| Figure 33: Offset PMCAP + 4h: PMCS – PCI Power Management Control and Status                         |    |

| Figure 34: Message Signaled Interrupt Capability (Optional)                                          |    |

| Figure 35: Offset MSICAP: MID – Message Signaled Interrupt Identifiers                               |    |

| Figure 37: Offset MSICAP + 4h: MA – Message Signaled Interrupt Message Control                       |    |

| Figure 38: Offset MSICAP + 8h: MUA – Message Signaled Interrupt Upper Address                        |    |

| Figure 39: Offset MSICAP + Ch: MD – Message Signaled Interrupt Message Data                          |    |

| Figure 40: Offset MSICAP + 10h: MMASK – Message Signaled Interrupt Mask Bits (Optional)              |    |

| Figure 41: Offset MSICAP + 14h: MPEND – Message Signaled Interrupt Pending Bits (Optional)           | 24 |

| Figure 42: MSI-X Capability (Optional)                                                               | 24 |

| Figure 43: Offset MSIXCAP: MXID – MSI-X Identifiers                                                  |    |

| Figure 44: Offset MSIXCAP + 2h: MXC – MSI-X Message Control                                          |    |

| Figure 45: Offset MSIXCAP + 4h: MTAB – MSI-X Table Offset / Table BIR                                |    |

| Figure 46: Offset MSIXCAP + 8h: MPBA – MSI-X PBA Offset / PBA BIR                                    |    |

| Figure 47: PCI Express Capability                                                                    |    |

| Figure 48: Offset PXCAP: PXID – PCI Express Capability ID                                            | 26 |

| Figure 49: Offset PXCAP + 2h: PXCAP – PCI Express Capabilities                                       |    |

| Figure 50: Offset PXCAP + 4h: PXDCAP – PCI Express Device Capabilities                               |    |

| Figure 51: Offset PXCAP + 8h: PXDC – PCI Express Device Control                                      |    |

| Figure 52: Offset PXCAP + Ah: PXDS – PCI Express Device Status                                       |    |

| Figure 53: Offset PXCAP + Ch: PXLCAP – PCI Express Link Capabilities                                 |    |

| Figure 54: Offset PXCAP + 10h: PXLC – PCI Express Link Control                                       |    |

| Figure 55: Offset PXCAP + 12h: PXLS – PCI Express Link Status                                        |    |

| Figure 56: Offset PXCAP + 24h: PXDCAP2 – PCI Express Device Capabilities 2                           |    |

| Figure 57: Offset PXCAP + 28h: PXDC2 – PCI Express Device Control 2                                  |    |

| Figure 58: Advanced Error Reporting Capability (Optional)                                            |    |

| Figure 59: Offset AERCAP: AERID – AER Capability ID                                                  |    |

| Figure 60: Offset AERCAP + 4: AERUCES – AER Uncorrectable Error Status Register                      |    |

| r igure o r. Onset AENOAF + 6. AENOCEIVI — AEN ONCONECIADIE ENOI IVIASK REGISTEI                     | 32 |

# NVMe® over PCle® Transport Specification, Revision 1.0e

| Figure 62: Offset AERCAP + Ch: AERUCESEV – AER Uncorrectable Error Severity Register | 33 |

|--------------------------------------------------------------------------------------|----|

| Figure 63: Offset AERCAP + 10h: AERCES – AER Correctable Error Status Register       |    |

| Figure 64: Offset AERCAP + 14h: AERCEM – AER Correctable Error Mask Register         |    |

| Figure 65: Offset AERCAP + 18h: AERCC – AER Capabilities and Control Register        | 34 |

| Figure 66: Offset AERCAP + 1Ch: AERHL – AER Header Log Register                      |    |

| Figure 67: Offset AFRCAP + 38h: AFRTIP - AFR TIP Prefix Log Register (Ontional)      | 35 |

# 1 Introduction

### 1.1 Overview

NVM Express® (NVMe®) Base Specification defines an interface for host software to communicate with a non-volatile memory subsystem (NVM subsystem) over a variety of memory-based transports and message-based transports.

This document defines mappings of extensions defined in the NVM Express Base Specification to a specific NVMe Transport: PCI Express<sup>®</sup>.

### 1.2 Scope

Figure 1 shows the relationship of the NVM Express® NVMe® over PCIe® Transport Specification to other specifications within the NVMe Family of Specifications.

WAN Express Base

Specification

Specification

Specification

Specification

NVM Express Base

Specification

Transport Specifications

(e.g., PCle®, RDMA, TCP)

Figure 1: NVMe Family of Specifications

This specification supplements the NVM Express Base Specification. This specification defines additional data structures, features, log pages, commands, and/or status values. This specification also defines extensions to existing data structures, features, log pages, commands, and/or status values. This specification defines requirements and behaviors that are specific to the PCIe transport. Functionality that is applicable generally to NVMe or that is applicable across multiple NVMe transports is defined in the NVM Express Base Specification.

If a conflict arises among requirements defined in different specifications, then a lower-numbered specification in the following list shall take precedence over a higher-numbered specification:

- 1. Non-NVMe specifications

- 2. NVM Express Base Specification

- 3. NVMe transport specifications

- 4. NVMe I/O command set specifications

- 5. NVM Express Management Interface Specification

### 1.3 Conventions

This specification conforms to the Conventions section of the NVM Express Base Specification with the following exception.

Inside sections that reference registers or properties, the following terms and abbreviations are different from the NVM Express Base Specification:

**Reset** This column indicates the value of the field after a reset as defined by the appropriate PCI or PCI Express specifications.

### 1.4 Definitions

### 1.4.1 Definitions from the NVM Express Base Specification

This specification uses the definitions in the NVM Express Base Specification.

### 1.5 References

NVM Express® (NVMe®) Base Specification revision 2.0. Available from https://www.nvmexpress.org.

PCI Bus Power Management Interface Specification Revision 1.2. Available from https://www.pcisig.com.

PCI Express Base Specification, Revision 4.0. Available from https://www.pcisig.com.

PCI-to-PCI Bridge Architecture Specification, Revision 1.2. Available from https://www.pcisig.com.

Advanced Configuration and Power Interface (ACPI) Specification, Version 6.4, January 2021. Available from https://www.uefi.org.

# 2 Transport Overview

The PCIe transport provides reliable mechanisms for memory mapped data transfer of Admin and I/O command data through memory mapped I/O transactions. The PCIe transport uses common PCIe capabilities such as:

- Memory mapped I/O for data transfer and register access;

- PCIe configuration space and

- PCIe message-based interrupts.

Refer to the PCIe specifications for a description of the details of PCIe.

Figure 2: Example of Transport Protocol Layers

# 3 Transport Binding

### 3.1 Setup & Initialization

This section describes the PCI Express register values when PCI Express is the transport.

### 3.1.1 PCI Device Requirements

This section details how the PCI Header, PCI Capabilities, and PCI Express Extended Capabilities should be constructed for an NVM Express controller. The fields shown are duplicated from the appropriate PCI or PCI Express specifications. The PCI documents are the normative specifications for these registers and this section details additional requirements for an NVM Express controller. Figure 3 lists the PCI Express defined register structures. Additional NVM Express requirements are defined in section 3.8.

Start End Name Type 00h 3Fh PCI Header PCI Capability **PMCAP** PMCAP+7h PCI Power Management Capability **MSICAP** MSICAP+9h Message Signaled Interrupt Capability **PCI** Capability MSIXCAP+Bh **MSIXCAP** MSI-X Capability **PCI** Capability PXCAP PXCAP+29h **PCI Express Capability PCI** Capability **AERCAP** AERCAP+47h Advanced Error Reporting Capability PCI Express Extended Capability

Figure 3: PCI Express Registers

MSI-X is the recommended interrupt mechanism. However, some systems may not support MSI-X. As a result, devices may choose to support both the MSI Capability and the MSI-X Capability.

The PCI and PCI Express registers described in section 3.8 are initialized based on the system configuration. This includes configuration of power management features. A single interrupt (e.g., pin-based, single MSI, or single MSI-X) should be used until the number of I/O Queues is determined.

### 3.1.2 Transport Specific Controller Properties

This section details the register definitions within the transport specific section of the Controller Properties table (refer to the Controller Properties section in the NVM Express Base Specification). Usage of these registers is described in section 3.3.

The PCIe transport supports Controller Properties as memory mapped registers that are located in the address range specified in the MLBAR/MUBAR registers (PCI BAR0 and BAR1). NVM Express defined registers for the PCI Express transport start at the offset defined in Figure 4. All controller registers shall be mapped to a memory space that supports in-order access and variable access widths. For many computer architectures, specifying the memory space as uncacheable produces this behavior. The host shall not issue locked accesses to registers. The host shall access registers in their native width or aligned 32-bit accesses. Violation of either of these host requirements results in undefined behavior.

Accesses that target any portion of two or more registers are not supported.

All reserved registers and all reserved bits within registers are read-only and return 0h when read.

| Start                             | End                               | Symbol  | Controller <sup>1</sup> | Name                                     |

|-----------------------------------|-----------------------------------|---------|-------------------------|------------------------------------------|

| 1000h                             | 1003h                             | SQ0TDBL | М                       | Submission Queue 0 Tail Doorbell (Admin) |

| 1000h + (1 *<br>(4 << CAP.DSTRD)) | 1003h + (1 *<br>(4 << CAP.DSTRD)) | CQ0HDBL | М                       | Completion Queue 0 Head Doorbell (Admin) |

| 1000h + (2 *<br>(4 << CAP.DSTRD)) | 1003h + (2 *<br>(4 << CAP.DSTRD)) | SQ1TDBL | 0                       | Submission Queue 1 Tail<br>Doorbell      |

| 1000h + (3 *<br>(4 << CAP.DSTRD)) | 1003h + (3 *<br>(4 << CAP.DSTRD)) | CQ1HDBL | 0                       | Completion Queue 1 Head Doorbell         |

Figure 4: PCI Express Specific Controller Property Definitions

Figure 4: PCI Express Specific Controller Property Definitions

| Start                                                                                     | End                                         | Symbol  | Controller <sup>1</sup> | Name                                |  |  |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------|---------|-------------------------|-------------------------------------|--|--|--|

| 1000h + (4 *<br>(4 << CAP.DSTRD))                                                         | 1003h + (4 *<br>(4 << CAP.DSTRD))           | SQ2TDBL | 0                       | Submission Queue 2 Tail Doorbell    |  |  |  |

| 1000h + (5 *<br>(4 << CAP.DSTRD))                                                         | 1003h + (5 *<br>(4 << CAP.DSTRD))           | CQ2HDBL | 0                       | Completion Queue 2 Head Doorbell    |  |  |  |

|                                                                                           |                                             |         |                         |                                     |  |  |  |

| 1000h+ (2y * (4 << CAP.DSTRD))                                                            | 1003h + (2y * (4 <<<br>CAP.DSTRD))          | SQyTDBL | 0                       | Submission Queue y Tail<br>Doorbell |  |  |  |

| 1000h +<br>((2y + 1) * (4 <<<br>CAP.DSTRD))                                               | 1003h +<br>((2y + 1) * (4 <<<br>CAP.DSTRD)) | CQyHDBL | 0                       | Completion Queue y Head<br>Doorbell |  |  |  |

| Notes:  1. O = Optional, M = Mandatory, R = Reserved. Applicable to all controller types. |                                             |         |                         |                                     |  |  |  |

### 3.1.2.1 Offset (1000h + ((2y) \* (4 << CAP.DSTRD))): SQyTDBL - Submission Queue y Tail Doorbell

This register defines the doorbell register that updates the Tail entry pointer for Submission Queue y. The value of y is equivalent to the Queue Identifier. This indicates to the controller that new commands have been submitted for processing.

The host should not read the doorbell registers. If a doorbell register is read, the value returned is vendor specific. Writing to a non-existent Submission Queue Tail Doorbell has undefined results.

Figure 5: Offset (1000h + ((2y) \* (4 << CAP.DSTRD))): SQyTDBL - Submission Queue y Tail Doorbell

| Bits  | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | 0h    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 15:00 | RW   | 0h    | Submission Queue Tail (SQT): Indicates the new value of the Submission Queue Tail entry pointer. This value shall overwrite any previous Submission Queue Tail entry pointer value provided. The difference between the last SQT entry pointer write and the current SQT entry pointer write indicates the number of commands added to the Submission Queue.  Note: Submission Queue rollover needs to be accounted for. |

# 3.1.2.2 Offset (1000h + ((2y + 1) \* (4 << CAP.DSTRD))): CQyHDBL - Completion Queue y Head Doorbell

This register defines the doorbell register that updates the Head entry pointer for Completion Queue y. The value of y is equivalent to the Queue Identifier. This indicates Completion Queue entries that have been processed by host software.

The host should not read the doorbell registers. If a doorbell register is read, the value returned is vendor specific. Writing to a non-existent Completion Queue Head Doorbell has undefined results.

Host software should continue to process Completion Queue entries within Completion Queues regardless of whether there are entries available in a particular or any Submission Queue.

Figure 6: Offset (1000h + ((2y + 1) \* (4 << CAP.DSTRD))): CQyHDBL - Completion Queue y Head Doorbell

| Bits  | Туре | Reset | Description |

|-------|------|-------|-------------|

| 31:16 | RO   | 0h    | Reserved    |

Figure 6: Offset (1000h + ((2y + 1) \* (4 << CAP.DSTRD))): CQyHDBL - Completion Queue y Head Doorbell

| Bits  | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:00 | RW   | 0h    | Completion Queue Head (CQH): Indicates the new value of the Completion Queue Head entry pointer. This value shall overwrite any previous Completion Queue Head value provided. The difference between the last CQH entry pointer write and the current CQH entry pointer write indicates the number of entries that are now available for re-use by the controller in the Completion Queue.  Note: Completion Queue rollover needs to be accounted for. |

### 3.1.3 Administrative Controller Support

The PCIe transport allows an Administrative controller to have a dedicated NVMe management driver loaded through the use of an explicit PCI programming interface value (refer to CC.PI field in Figure 15).

### 3.2 Queue Model Instantiation

The NVM Express use of the PCIe transport is based on a paired Submission and Completion Queue mechanism. Commands are placed by host software into a Submission Queue. Completions are placed into the associated Completion Queue by the controller.

The NVM Express use of the PCIe transport supports multiple Submission Queues to utilize the same Completion Queue. Submission and Completion Queues are allocated in host-addressable memory.

When instantiating an I/O Completion Queue using the Create I/O Completion Queue command, the host specifies if interrupts will be enabled using the Interrupts Enabled (IEN) field. When interrupts are enabled a transport specific field, Interrupt Vector, shall also be initialized. The following definition of the Interrupt Vector field is used for the PCIe transport:

Figure 7: Create I/O Completion Queue - Command Dword 11

| Bits  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | Interrupt Vector (IV): This field indicates interrupt vector to use for this Completion Queue. This corresponds to the MSI-X or multiple message MSI vector to use. If using single message MSI or pin-based interrupts, then this field shall be cleared to 0h. In MSI-X, a maximum of 2,048 vectors are used. This value shall not be set to a value greater than the number of messages the controller supports (refer to MSICAP.MC.MME or MSIXCAP.MXC.TS). If the value is greater than the number of messages the controller supports, the controller should return an error of Invalid Interrupt Vector. |

### 3.3 Resets

### 3.3.1 Controller Level Reset

The following transport specific methods initiate a Controller Level Reset in addition to the methods described in the NVM Express Base Specification:

- Conventional Reset (refer to the PCI Express Base Specification); and

- Function Level Reset (refer to the PCI Express Base Specification)

In all Controller Level Reset cases except a Controller Reset (refer to the Controller Level Reset section of the NVM Express Base Specification), the PCI register space is reset as defined by the PCI Express Base Specification.

### 3.3.2 NVM Subsystem Reset

When an NVM Subsystem Reset occurs, all PCIe links in the NVM Subsystem transition to the LTSSM Detect state.

### 3.4 Data Transfer Model

The PCIe transport is a memory-based transport that uses memory operations directly for data transfer as described in the Memory Based Theory of Operations section of the NVM Express Base Specification.

### 3.4.1 Command Processing

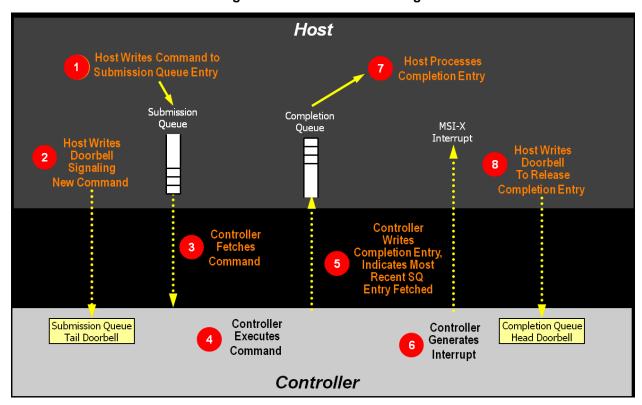

This section describes command submission and completion processing for the PCle transport. Figure 8 shows the steps to submit and complete a command. The steps are:

- 1. The host places one or more commands for execution in the next free Submission Queue slot(s) in memory;

- The host updates the Submission Queue Tail Doorbell register with the new value of the Submission Queue Tail entry pointer. This indicates to the controller that a new command(s) is submitted for processing;

- The controller transfers the command(s) in the Submission Queue slot(s) into the controller for future execution. Arbitration is the method used to determine the Submission Queue from which the controller starts processing the next candidate command(s), refer to the Command Arbitration section of the NVM Express Base Specification;

- 4. The controller then proceeds with execution of the next command(s). Commands may complete out of order:

- 5. After a command has completed execution, the controller places a Completion Queue entry in the next free slot in the associated Completion Queue. As part of the Completion Queue entry, the controller indicates the most recent Submission Queue entry that has been consumed by advancing the Submission Queue Head pointer in the completion entry. Each new Completion Queue entry has a Phase Tag inverted from the previous entry to indicate to the host that this Completion Queue entry is a new entry;

- 6. The controller optionally generates an interrupt to the host to indicate that there is a new Completion Queue entry to consume and process. In the figure, the interrupt is shown as an MSI-X interrupt, however, it could also be a pin-based or MSI interrupt. Note that based on interrupt coalescing settings, an interrupt may or may not be generated for each new Completion Queue entry;

- 7. The host consumes and then processes the new Completion Queue entries in the Completion Queue. This includes taking any actions based on error conditions indicated. The host continues consuming and processing Completion Queue entries until a previously consumed entry with a Phase Tag inverted from the value of the current Completion Queue entries is encountered; and

- 8. The host writes the Completion Queue Head Doorbell register to indicate that the Completion Queue entry has been consumed. The host may consume many entries before updating the associated Completion Queue Head Doorbell register.

Figure 8: Command Processing

### 3.4.2 Command Related Resource Retirement

As part of reporting completions, the controller indicates the most recent Submission Queue entry that has been consumed. Submission Queue slots containing consumed Submission Queue entries are free and may be re-used by host software to submit new commands.

If a Completion Queue entry is posted for a command, then host software may re-use the associated PRP List(s) for that command and other resources (an exception is the PRP List for I/O Submission Queues and I/O Completion Queues).

### 3.5 Interrupts

The interrupt architecture allows for efficient reporting of interrupts such that the host may service interrupts through the least amount of overhead.

The specification allows the controller to be configured to report interrupts in one of four modes. The four modes are: pin-based interrupt, single message MSI, multiple message MSI, and MSI-X. It is recommended that MSI-X be used whenever possible to enable higher performance, lower latency, and lower CPU utilization for processing interrupts.

Interrupt aggregation, also referred to as interrupt coalescing, mitigates host interrupt overhead by reducing the rate at which interrupt requests are generated by a controller. This reduced host overhead typically comes at the expense of increased latency. Rather than prescribe a specific interrupt aggregation algorithm, this specification defines the mechanisms a host may use to communicate interrupt aggregation parameters to a controller and leaves the specific interrupt aggregation algorithm used by a controller as vendor specific. Interrupts associated with the Admin Completion Queue should not be delayed.

The Aggregation Threshold field in the Interrupt Coalescing feature (refer to the Interrupt Coalescing feature within the NVM Express Base Specification) specifies the minimum interrupt aggregation threshold on a per vector basis. This value defines the number of Completion Queue entries that when aggregated on a per interrupt vector basis reduces host interrupt processing overhead below a host determined threshold.

This value is provided to the controller as a recommendation by the host and a controller is free to generate an interrupt before or after this aggregation threshold is achieved. The specific manner in which this value is used by the interrupt aggregation algorithm implemented by a controller is implementation specific.

The Aggregation Time field in the Interrupt Coalescing feature (refer to the Interrupt Coalescing feature within the NVM Express Base Specification) specifies the maximum delay that a controller may apply to a Completion Queue entry before an interrupt is signaled to the host. This value is provided to the controller as a recommendation by the host and a controller is free to generate an interrupt before or after this aggregation time is achieved. A controller may apply this value on a per vector basis or across all vectors. The specific manner in which this value is used by the interrupt aggregation algorithm implemented by a controller is implementation specific.

Although support of the Get Features and Set Features commands associated with interrupt coalescing is required for PCIe-based NVMe controller implementations, the manner in which the Aggregation Threshold and Aggregation Time fields are used is implementation specific. For example, an implementation may ignore these fields and not implement interrupt coalescing.

### 3.5.1 Pin Based, Single MSI, and Multiple MSI Behavior

This is the mode of interrupt operation if any of the following conditions are met:

- Pin-based interrupts are being used MSI (i.e., MSICAP.MC.MSIE='0') and MSI-X are disabled;

- Single MSI is being used MSI is enabled (i.e., MSICAP.MC.MSIE='1'), MSICAP.MC.MME=000b, and MSI-X is disabled; or

- Multiple MSI is being used multiple message MSI is enabled (i.e., MSICAP.MC.MSIE='1'), MSICAP.MC.MME is set to a value between 001b and 101b inclusive, and MSI-X is disabled.

Within the controller there is an interrupt status register (IS) that is not visible to the host. In this mode, the IS register determines whether the PCI interrupt line shall be driven active or an MSI message shall be sent. Each bit in the IS register corresponds to an interrupt vector. The IS bit is set to '1' when the following conditions are true:

- There is one or more unacknowledged Completion Queue entries in a Completion Queue that utilizes this interrupt vector;

- The Completion Queue(s) with unacknowledged Completion Queue entries has interrupts enabled in the Create I/O Completion Queue command; and

- The corresponding INTM bit exposed to the host is cleared to '0', indicating that the interrupt is not masked.

For single and multiple MSI, the INTM register masks interrupt delivery prior to MSI logic. As such, an interrupt on a vector masked by INTM does not cause the corresponding Pending bit to assert within the MSI Capability Structure.

If MSIs are not enabled, IS[0] being set to '1' causes the PCI interrupt line to be active (electrical '0'). If MSIs are enabled, any change to the IS register that causes an unmasked status bit to transition from '0' to '1' or clearing of a mask bit to '0' whose corresponding status bit is set to '1' shall cause an MSI to be sent. Therefore, while in wire mode, a single wire remains active, while in MSI mode, several messages may be sent, as each edge triggered event on a port shall cause a new message.

If pin-based interrupts or single message MSI interrupts are used, host software interrogates the Completion Queue(s) for new completion queue entries. If multiple message MSI is in use, then the interrupt vector indicates the Completion Queue(s) with possible new command completions for the host to process.

To clear an interrupt for a particular interrupt vector, host software acknowledges all Completion Queue entries for Completion Queues associated with the interrupt vector by updating the CQ Head doorbell register (refer to the Memory-Based Transport Model section in the NVM Express Base Specification).

Figure 9: Pin Based, Single MSI, and Multiple MSI Behavior

| Status of IS Register                                                                                                                                                         | Pin-based Action | MSI Action       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|

| All bits '0'  Note: May be caused by corresponding bit(s) in the INTM register being set to '1', masking the corresponding interrupt.                                         | Wire inactive    | No action        |

| One or more bits set to '1'  Note: May be caused by corresponding bit(s) in the INTM register being cleared to '0', unmasking the corresponding interrupt.                    | Wire active      | New message sent |

| One or more bits set to '1', new bit gets set to '1'                                                                                                                          | Wire active      | New message sent |

| One or more bits set to '1', some (but not all) bits in the IS register are cleared to '0' (i.e., host software acknowledges some of the associated Completion Queue entries) | Wire active      | New message sent |

| One or more bits set to '1', all bits in the IS register are cleared to '0' (i.e., host software acknowledges all associated Completion Queue entries)                        | Wire inactive    | No action        |

### 3.5.1.1 Differences Between Pin Based and MSI Interrupts

Single MSI is similar to the pin-based interrupt behavior mode. The primary difference is the method of reporting the interrupt. Instead of communicating the interrupt through an INTx virtual wire, an MSI message is generated to the host. Unlike INTx virtual wire interrupts which are level sensitive, MSI interrupts are edge sensitive.

Pin-based and single MSI only use one interrupt vector. Multiple MSI may use up to 32 interrupt vectors.

For multiple MSI, the controller advertises the requested number of MSI interrupt vectors in the Multiple Message Capable (MMC) field in the Message Signaled Interrupt Message Control (MC) register. The MSICAP.MC.MMC field represents a power-of-2 wrapper on the number of requested vectors. For example, if three vectors are requested, then the MSICAP.MC.MMC field shall be '010' (i.e., four vectors).

Multiple-message MSI allows completions to be aggregated on a per vector basis. If sufficient MSI vectors are allocated, each Completion Queue(s) may send its own interrupt message, as opposed to a single message for all completions.

### 3.5.2 MSI-X Based Behavior

MSI-X is the preferred interrupt behavior to use. The following configuration describes this mode of interrupt operation:

- Multiple-message MSI is disabled (i.e., MSICAP.MC.MSIE is cleared to '0' and MSICAP.MC.MME is cleared to 000b); and

- MSI-X is enabled.

MSI-X, similar to multiple-message MSI, allows completions to be aggregated on a per vector basis. However, the maximum number of vectors is 2KiB. MSI-X also allows each interrupt to send a unique message data corresponding to the vector.

MSI-X allows completions to be aggregated on a per vector basis. Each Completion Queue(s) may send its own interrupt message, as opposed to a single message for all completions.

When generating an MSI-X message, the following checks occur before generating the message:

- The Function Mask bit in the MSI-X Message Control register is cleared to '0'; and

- The corresponding vector mask in the MSI-X table structure is cleared to '0'.

If either of the mask bits are set to '1', the corresponding pending bit in the MSI-X PBA structure is set to '1' to indicate that an interrupt is pending for that vector. The MSI for that vector is later generated when both the mask bits are cleared to '0'.

It is recommended that the interrupt vector associated with the CQ(s) being processed be masked during processing of Completion Queue entries within the CQ(s) to avoid spurious and/or lost interrupts. The interrupt mask table defined as part of MSI-X should be used to mask interrupts.

The interrupt vector indicates the Completion Queue(s) with possible new command completions for the host to process.

### 3.6 Power Management

Power Management operates as defined in the NVM Express Base Specification with the following specifics for the PCI etransport (refer to the PCI Express Base Specification and the PCI Bus Power Management Interface Specification).

In this specification, RTD3 refers to the  $D3_{cold}$  power state described in the PCI Express Base Specification. RTD3 does not include the PCI Express  $D3_{hot}$  power state because main power is not removed from the controller in the  $D3_{hot}$  power state. Refer to the PCI Express Base Specification for details on the  $D3_{hot}$  power state and the  $D3_{cold}$  power state.

The host shall never select a power state (refer to the Power State Descriptors in the Identify Controller data in the NVM Express Base Specification) that consumes more power than the PCI Express slot power limit control value expressed by the Captured Slot Power Limit Value (CSPLV) and Captured Slot Power Limit Scale (CSPLS) fields of the PCI Express Device Capabilities (PXDCAP) register. Hosts that do not dynamically manage power should set the power state to the lowest numbered state that satisfies the PCI Express slot power limit control value.

If a controller implements the PCI Express Dynamic Power Allocation (DPA) capability and that capability is enabled (i.e., the Substate Control Enable bit is set to '1'), then the maximum power that may be consumed by the NVM subsystem is equal to the minimum value specified by the DPA substate or the NVM Express power state, whichever is lower.

### 3.7 Error Handling Model

It is recommended that implementations support the Advanced Error Reporting Capability to enable more robust error handling.

### 3.8 Transport Specific Content

### 3.8.1 PCI Express Type 0/1 Common Configuration Space

Figure 10 summarizes the organization of the Type 0/1 Common Configuration Space defined in the PCI Express Base Specification. The reference information in this section does not contain all PCI Express requirements. Refer to the PCI Express Base Specification for more information.

| Start | End | Symbol          | Name                                                         | Reference |

|-------|-----|-----------------|--------------------------------------------------------------|-----------|

| 00h   | 03h | ID              | Identifiers                                                  | 3.8.1.1   |

| 04h   | 05h | CMD             | Command Register                                             | 3.8.1.2   |

| 06h   | 07h | STS             | Device Status                                                | 3.8.1.3   |

| 08h   | 08h | RID             | Revision ID                                                  | 3.8.1.4   |

| 09h   | 0Bh | CC              | Class Codes                                                  | 3.8.1.5   |

| 0Ch   | 0Ch | CLS             | Cache Line Size                                              | 3.8.1.6   |

| 0Dh   | 0Dh | MLT             | Master Latency Timer                                         | 3.8.1.7   |

| 0Eh   | 0Eh | HTYPE           | Header Type                                                  | 3.8.1.8   |

| 0Fh   | 0Fh | BIST            | Built-In Self Test (Optional)                                | 3.8.1.9   |

| 10h   | 13h | MLBAR<br>(BAR0) | Memory Register Base Address, lower 32-bits<br><bar0></bar0> | 3.8.1.10  |

| 14h   | 17h | MUBAŔ<br>(BAR1) | Memory Register Base Address, upper 32-bits <bar1></bar1>    | 3.8.1.11  |

Figure 10: PCI Express Type 0/1 Common Configuration Space

Figure 10: PCI Express Type 0/1 Common Configuration Space

| Start | End | Symbol | Name                                                                                    | Reference |

|-------|-----|--------|-----------------------------------------------------------------------------------------|-----------|

| 18h   | 1Bh | BAR2   | Index/Data Pair Register Base Address or<br>Vendor Specific (Optional)<br><bar2></bar2> | 3.8.1.12  |

| 1Ch   | 1Fh | BAR3   | Vendor Specific                                                                         | 3.8.1.13  |

| 20h   | 23h | BAR4   | Vendor Specific                                                                         | 3.8.1.14  |

| 24h   | 27h | BAR5   | Vendor Specific                                                                         | 3.8.1.15  |

| 28h   | 2Bh | CCPTR  | CardBus CIS Pointer                                                                     | 3.8.1.16  |

| 2Ch   | 2Fh | SS     | Subsystem Identifiers                                                                   | 3.8.1.17  |

| 30h   | 33h | EROM   | Expansion ROM Base Address (Optional)                                                   | 3.8.1.18  |

| 34h   | 34h | CAP    | Capabilities Pointer                                                                    | 3.8.1.19  |

| 35h   | 3Bh | R      | Reserved                                                                                |           |

| 3Ch   | 3Dh | INTR   | Interrupt Information                                                                   | 3.8.1.20  |

| 3Eh   | 3Eh | MGNT   | Minimum Grant (Optional)                                                                | 3.8.1.21  |

| 3Fh   | 3Fh | MLAT   | Maximum Latency (Optional)                                                              | 3.8.1.22  |

# 3.8.1.1 Offset 00h: ID - Identifiers

Figure 11: Offset 00h: ID - Identifiers

| Bits  | Туре | Reset        | Description                                                                                  |

|-------|------|--------------|----------------------------------------------------------------------------------------------|

| 31:16 | RO   | Impl         | <b>Device ID (DID):</b> Indicates the device number assigned by the vendor. Specific to each |

| 31.10 | KU   | Spec         | implementation.                                                                              |

| 15:00 | RO   | Impl<br>Spec | Vendor ID (VID): Indicates the company vendor, assigned by the PCI SIG.                      |

# 3.8.1.2 Offset 04h: CMD - Command

Figure 12: Offset 04h: CMD - Command

| Bits  | Type  | Reset | Description                                                                                                                                                                                                                            |

|-------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 | RO    | 0h    | Reserved by PCI-SIG®                                                                                                                                                                                                                   |

| 10    | RW    | 0b    | Interrupt Disable (ID): Disables the controller from generating pin-based INTx# interrupts. This bit does not have any effect on MSI or MSI-X operation.                                                                               |

| 09    | RO    | 0b    | Fast Back-to-Back Enable (FBE): Not supported by the NVM Express interface.                                                                                                                                                            |

| 08    | RW/RO | 0b    | SERR# Enable (SEE): Controls error reporting.                                                                                                                                                                                          |

| 07    | RO    | 0b    | Reserved by PCI-SIG                                                                                                                                                                                                                    |

| 06    | RW/RO | 0b    | <b>Parity Error Response Enable (PEE):</b> When set to '1', the controller shall generate PERR# when a data parity error is detected. If parity is not supported, then this bit is read-only '0'.                                      |

| 05    | RO    | 0b    | VGA Palette Snooping Enable (VGA): Shall be cleared to zero for NVM Express use.                                                                                                                                                       |

| 04    | RO    | 0b    | <b>Memory Write and Invalidate Enable (MWIE):</b> Shall be cleared to zero for NVM Express use.                                                                                                                                        |

| 03    | RO    | 0b    | Special Cycle Enable (SCE): Shall be cleared to zero for NVM Express use.                                                                                                                                                              |

| 02    | RW    | 0b    | <b>Bus Master Enable (BME):</b> Enables the controller to act as a master for data transfers. When set to '1', bus master activity is allowed. When cleared to '0', the controller is not allowed to issue any Memory or I/O Requests. |

| 01    | RW    | 0b    | <b>Memory Space Enable (MSE):</b> Controls access to the controller's register memory space.                                                                                                                                           |

| 00    | RW    | 0b    | I/O Space Enable (IOSE): Controls access to the controller's target I/O space.                                                                                                                                                         |

### 3.8.1.3 Offset 06h: STS - Device Status

Figure 13: Offset 06h: STS - Device Status

| Bits  | Туре   | Reset | Description                                                                            |

|-------|--------|-------|----------------------------------------------------------------------------------------|

| 15    | RWC    | 0b    | Detected Parity Error (DPE): Set to '1' by hardware when the controller detects a      |

| 15    | KVVC   | OD    | parity error on its interface.                                                         |

| 14    | RWC/RO | 0b    | Signaled System Error (SSE): Refer to the PCI SIG specifications.                      |

| 13    | RWC    | 0b    | Received Master-Abort (RMA): Set to '1' by hardware when the controller receives       |

| 13    | KVVC   | OD    | a master abort to a cycle the controller generated.                                    |

| 12    | RWC    | 0b    | Received Target Abort (RTA): Set to '1' by hardware when the controller receives a     |

| 12    | KVVC   | OD    | target abort to a cycle the controller generated.                                      |

| 11    | RO     | 0b    | Signaled Target-Abort (STA): Not supported by the NVM Express interface.               |

| 10:09 | RO     | Impl  | <b>DEVSEL# Timing (DEVT):</b> Controls the device select time for the controller's PCI |

| 10.09 | KO     | Spec  | interface. This field is not applicable to PCI Express implementations.                |

|       |        |       | Master Data Parity Error Detected (DPD): Set to '1' by hardware when the               |

| 08    | RWC    | 0b    | controller, as a master, either detects a parity error or sees the parity error line   |

|       |        |       | asserted, and the Parity Error Response Enable bit (CMD.PEE) is set to '1'.            |

| 07    | RO     | Impl  | Fast Back-to-Back Capable (FBC): Shall be cleared to zero for NVM Express use.         |

|       |        | Spec  | · · · · · · · · · · · · · · · · · · · ·                                                |

| 06    | RO     | 0b    | Reserved by PCI-SIG                                                                    |

| 05    | RO     | Impl  | 66 MHz Capable (C66): Shall be cleared to zero for NVM Express use.                    |

| 00    | RO     | Spec  | oo iii 12 Capable (Coo). Shall be dealed to zelo for 14410 Express use.                |

| 04    | RO     | 1b    | Capabilities List (CL): Indicates the presence of a capabilities list. The controller  |

|       |        |       | shall support the PCI Power Management capability as a minimum.                        |

| 03    | RO     | 0     | Interrupt Status (IS): Indicates the interrupt status of the device ('1' = asserted).  |

| 02:00 | RO     | 000b  | Reserved by PCI-SIG                                                                    |

### 3.8.1.4 Offset 08h: RID - Revision ID

Figure 14: Offset 08h: RID - Revision ID

| Bits  | Туре | Reset        | Description                                                       |

|-------|------|--------------|-------------------------------------------------------------------|

| 07:00 | RO   | Impl<br>Spec | Revision ID (RID): Indicates stepping of the controller hardware. |

### 3.8.1.5 Offset 09h: CC - Class Code

Fields in the Class Code register are described in the PCI Code and ID Assignment Specification.

Figure 15: Offset 09h: CC - Class Code

| Bits  | Type | Reset            | Description                                                                                                                                                                                                                                                          |

|-------|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23:16 | RO   | 01h              | Base Class Code (BCC): Indicates the base class code as a mass storage controller.                                                                                                                                                                                   |

| 15:08 | RO   | 08h              | <b>Sub Class Code (SCC):</b> Indicates the sub class code as a Non-Volatile Memory controller.                                                                                                                                                                       |

| 07:00 | RO   | 02h<br>or<br>03h | <b>Programming Interface (PI):</b> This field specifies that the controller uses the NVM Express programming interface. I/O Controllers shall report 02h and Administrative controllers shall report 03h as defined by the PCI Code and ID Assignment Specification. |

### 3.8.1.6 Offset 0Ch: CLS - Cache Line Size

Figure 16: Offset 0Ch: CLS - Cache Line Size

| Bits  | Туре | Reset | Description                                                                      |

|-------|------|-------|----------------------------------------------------------------------------------|

| 07:00 | RW   | 00h   | Cache Line Size (CLS): Cache Line Size register is set by the system firmware or |

| 07.00 | 1    | 0011  | operating system to the system cache size.                                       |

### 3.8.1.7 Offset 0Dh: MLT - Master Latency Timer

Figure 17: Offset 0Dh: MLT - Master Latency Timer

| Bits  | Type | Reset | Description                                                                                                                                                                                                  |

|-------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07:00 | RO   | 00h   | <b>Master Latency Timer (MLT):</b> Indicates the number of clocks the controller is allowed to act as a master on PCI. For a PCI Express device, this register does not apply and shall be hardwired to '0'. |

### 3.8.1.8 Offset 0Eh: HTYPE - Header Type

Figure 18: Offset 0Eh: HTYPE - Header Type

| Bits  | Туре | Reset | Description                                                                               |

|-------|------|-------|-------------------------------------------------------------------------------------------|

| 07    | RO   | Impl  | Multi-Function Device (MFD): Indicates whether the controller is part of a multi-function |

| 07    | KU   | Spec  | device.                                                                                   |

| 06:00 | RO   | 00h   | Header Layout (HL): Indicates that the controller uses a target device layout.            |

### 3.8.1.9 Offset 0Fh: BIST - Built-In Self Test (Optional)

The following register is optional, but if implemented, shall look as follows. When not implemented, the register shall be read-only returning the value 0h.

Figure 19: Offset 0Fh: BIST - Built-In Self Test (Optional)

| Bits  | Type | Reset        | Description                                                                                                                             |

|-------|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 07    | RO   | Impl<br>Spec | BIST Capable (BC): Indicates whether the controller has a BIST function.                                                                |

| 06    | RW   | 0b           | <b>Start BIST (SB):</b> Host software sets this bit to '1' to invoke BIST. The controller clears this bit to '0' when BIST is complete. |

| 05:04 | RO   | 00b          | Reserved                                                                                                                                |

| 03:00 | RO   | 0h           | <b>Completion Code (CC):</b> Indicates the completion code status of BIST. A non-zero value indicates a failure.                        |

### 3.8.1.10 Offset 10h: MLBAR (BAR0) - Memory Register Base Address, lower 32-bits

This register allocates space for the controller properties defined in the Controller Properties section of the NVM Express Base Specification.

Figure 20: Offset 10h: MLBAR (BAR0) - Memory Register Base Address, lower 32-bits

| Bits  | Type | Reset        | Description                                                                                                                                                                                                                                                                 |

|-------|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:14 | RW   | 0h           | <b>Base Address (BA):</b> Base address of register memory space. For controllers that support a larger number of doorbell registers or have vendor specific space following the doorbell registers, more bits are allowed to be RO such that more memory space is consumed. |

| 13:04 | RO   | 0h           | Reserved by PCI-SIG                                                                                                                                                                                                                                                         |

| 03    | RO   | 0b           | Prefetchable (PF): Indicates that this range is not prefetchable.                                                                                                                                                                                                           |

| 02:01 | RO   | Impl<br>Spec | <b>Type (TP):</b> Indicates where this range may be mapped. It is recommended to support mapping anywhere in 64-bit address space.                                                                                                                                          |

| 00    | RO   | 0b           | Resource Type Indicator (RTE): Indicates a request for register memory space.                                                                                                                                                                                               |

### 3.8.1.11 Offset 14h: MUBAR (BAR1) - Memory Register Base Address, upper 32-bits

This register specifies the upper 32-bit address of the controller properties defined in the Controller Properties section of the NVM Express Base Specification.

Figure 21: Offset 14h: MUBAR (BAR1) - Memory Register Base Address, upper 32-bits

| Bits  | Туре | Reset | Description                                                                        |

|-------|------|-------|------------------------------------------------------------------------------------|

| 31:00 | RW   | 0h    | Base Address (BA): Upper 32-bits (bits 63:32) of the memory register base address. |

Note: NVM Express implementations that reside behind PCI compliant bridges, such as PCI Express Endpoints, are restricted to having 32-bit assigned base address registers due to limitations on the maximum address that may be specified in the bridge for non-prefetchable memory. Refer to the PCI-to-PCI Bridge Architecture Specification 1.2 for more information on this restriction.

# 3.8.1.12 Offset 18h: BAR2 – Index/Data Pair Register Base Address or Vendor Specific (Optional)

If this register is configured as I/O space, then this register specifies the Index/Data Pair base address and is configured as shown in Figure 22. These registers are used to access the controller properties defined in defined in the Controller Properties section of the NVM Express Base Specification using I/O based accesses.

Figure 22: Offset 18h: BAR2 – Index/Data Pair Register Base Address or Vendor Specific (Optional)

| Bits  | Туре | Reset | Description                                                                           |

|-------|------|-------|---------------------------------------------------------------------------------------|

| 31:03 | RW   | 0h    | Base Address (BA): Base address of Index/Data Pair registers that is 8 bytes in size. |

| 02:01 | RO   | 00b   | Reserved                                                                              |

| 00    | RO   | 1b    | Resource Type Indicator (RTE): Indicates a request for register I/O space.            |

If this register is configured as memory space (Resource Type Indicator is cleared to '0'), then the BAR2 register is vendor specific. Vendor specific space may also be allocated at the end of the controller properties defined in the Controller Properties section of the NVM Express Base Specification.

### 3.8.1.13 Offset 1Ch to 1Fh: BAR3 - Vendor Specific

The BAR3 register is vendor specific. Vendor specific space may also be allocated at the end of the controller properties defined in the Controller Properties section of the NVM Express Base Specification.

### 3.8.1.14 Offset 20h to 23h: BAR4 - Vendor Specific

The BAR4 register is vendor specific. Vendor specific space may also be allocated at the end of the controller properties defined in the Controller Properties section of the NVM Express Base Specification.

### 3.8.1.15 Offset 24h to 27h: BAR5 - Vendor Specific

The BAR5 register is vendor specific. Vendor specific space may also be allocated at the end of the controller properties defined in the Controller Properties section of the NVM Express Base Specification.

### 3.8.1.16 Offset 28h: CCPTR - CardBus CIS Pointer

Figure 23: Offset 28h: CCPTR - CardBus CIS Pointer

| Ī | Bits  | Type | Reset | Description                                   |

|---|-------|------|-------|-----------------------------------------------|

| Ī | 31:00 | RO   | 0h    | Shall be cleared to zero for NVM Express use. |

### 3.8.1.17 Offset 2Ch: SS - Subsystem Identifiers

Figure 24: Offset 2Ch: SS - Subsystem Identifiers

| Bits  | Type | Reset  | Description                                                            |

|-------|------|--------|------------------------------------------------------------------------|

| 31:16 | RO   | HwInit | Subsystem ID (SSID): Indicates the subsystem identifier.               |

| 15:00 | RO   | HwInit | Subsystem Vendor ID (SSVID): Indicates the subsystem vendor identifier |

### 3.8.1.18 Offset 30h: EROM - Expansion ROM (Optional)

If the register is not implemented, the register shall be read-only returning the value 0h.

Figure 25: Offset 30h: EROM – Expansion ROM (Optional)

| Bits  | Туре | Reset | Description                                                                      |  |

|-------|------|-------|----------------------------------------------------------------------------------|--|

| 31:00 | RW   | Impl  | ROM Base Address (RBA): Indicates the base address of the controller's expansion |  |

| 31.00 |      | Spec  | ROM. Not supported for integrated implementations.                               |  |

### 3.8.1.19 Offset 34h: CAP - Capabilities Pointer

Figure 26: Offset 34h: CAP - Capabilities Pointer

| Bits | Type | Reset        | Description                                                             |

|------|------|--------------|-------------------------------------------------------------------------|

| 7:0  | RO   | Impl<br>Spec | Capability Pointer (CP): Indicates the first capability pointer offset. |

### 3.8.1.20 Offset 3Ch: INTR - Interrupt Information

Figure 27: Offset 3Ch: INTR - Interrupt Information

| Bits  | Type | Reset        | Description                                                                                                                                                                       |

|-------|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:08 | RO   | Impl<br>Spec | Interrupt Pin (IPIN): This indicates the interrupt pin the controller uses.                                                                                                       |

| 07:00 | RW   | 0h           | <b>Interrupt Line (ILINE):</b> Host software written value to indicate which interrupt line (vector) the interrupt is connected to. No hardware action is taken on this register. |

### 3.8.1.21 Offset 3Eh: MGNT - Minimum Grant

Figure 28: Offset 3Eh: MGNT – Minimum Grant

| Bits  | Туре | Reset | Description                                              |

|-------|------|-------|----------------------------------------------------------|

| 07:00 | RO   | 0h    | Grant (GNT): Not supported by the NVM Express interface. |

### 3.8.1.22 Offset 3Fh: MLAT – Maximum Latency

Figure 29: Offset 3Fh: MLAT – Maximum Latency

| Bits  | Туре | Reset | Description                                                |

|-------|------|-------|------------------------------------------------------------|

| 07:00 | RO   | 0h    | Latency (LAT): Not supported by the NVM Express interface. |

### 3.8.2 PCI Power Management Capabilities

Refer to the Offset 14h: CC – Controller Configuration section in the NVM Express Base Specification for requirements when the PCI power management state changes.

Figure 30: PCI Power Management Capabilities

| Start    | End      | Symbol | Name                                    |

|----------|----------|--------|-----------------------------------------|

| PMCAP    | PMCAP+1h | PID    | PCI Power Management Capability ID      |

| PMCAP+2h | PMCAP+3h | PC     | PCI Power Management Capabilities       |

| PMCAP+4h | PMCAP+5h | PMCS   | PCI Power Management Control and Status |

### 3.8.2.1 Offset PMCAP: PID - PCI Power Management Capability ID

Figure 31: Offset PMCAP: PID - PCI Power Management Capability ID

| Bits  | Type | Reset        | Description                                                                                                                                                                                                |

|-------|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:08 | RO   | Impl<br>Spec | <b>Next Capability (NEXT):</b> Indicates the location of the next capability item in the list. This may be a capability pointer (such as Message Signaled Interrupts) or may be the last item in the list. |

| 07:00 | RO   | 1h           | Cap ID (CID): Indicates that this pointer is a PCI Power Management capability.                                                                                                                            |

# 3.8.2.2 Offset PMCAP + 2h: PC - PCI Power Management Capabilities

Figure 32: Offset PMCAP + 2h: PC - PCI Power Management Capabilities

| Bits  | Туре | Reset        | Description                                                                                                            |  |  |  |

|-------|------|--------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15:11 | RO   | 0h           | PME_Support (PSUP): Not supported by the NVM Express interface.                                                        |  |  |  |

| 10    | RO   | 0b           | <b>D2_Support (D2S):</b> Indicates support for the D2 power management state. Not recommended for implementation.      |  |  |  |

| 09    | RO   | 0b           | <b>D1_Support (D1S):</b> Indicates support for the D1 power management state. Not recommended for implementation.      |  |  |  |

| 08:06 | RO   | 000b         | Aux_Current (AUXC): Not supported by the NVM Express interface.                                                        |  |  |  |

| 05    | RO   | Impl<br>Spec | <b>Device Specific Initialization (DSI):</b> Indicates whether device specific initialization is required.             |  |  |  |

| 04    | RO   | 0b           | Reserved by PCI-SIG                                                                                                    |  |  |  |

| 03    | RO   | 0b           | PME Clock (PMEC): Indicates that PCI clock is not required to generate PME#.                                           |  |  |  |

| 02:00 | RO   | Impl<br>Spec | <b>Version (VS):</b> Indicates support for revision 1.2 or higher revisions of the PCI Power Management Specification. |  |  |  |

### 3.8.2.3 Offset PMCAP + 4h: PMCS – PCI Power Management Control and Status

Figure 33: Offset PMCAP + 4h: PMCS - PCI Power Management Control and Status

| Bits  | Type | Reset | Description                                                                                     |  |  |  |

|-------|------|-------|-------------------------------------------------------------------------------------------------|--|--|--|

| 15    | RWC  | 0b    | PME Status (PMES): Refer to the PCI SIG specifications.                                         |  |  |  |

| 14:13 | RO   | 00b   | Data Scale (DSC): Refer to the PCI SIG specifications.                                          |  |  |  |

| 12:09 | RO/  | 0h    | Data Select (DSE): If PME is not supported, then this field is read-only '0'. Refer to the      |  |  |  |

| 12.09 | RW   | UII   | PCI SIG specifications.                                                                         |  |  |  |

| 08    | RO/  | 0b    | <b>PME Enable (PMEE):</b> If PME is not supported, then this bit is read-only '0'. Refer to the |  |  |  |

| 00    | RW   | UD    | PCI SIG specifications.                                                                         |  |  |  |

| 07:04 | RO   | 0h    | Reserved by PCI-SIG                                                                             |  |  |  |

| 03    | RO   | 1b    | No Soft Reset (NSFRST): A value of '1' indicates that the controller transitioning from         |  |  |  |

| 03    |      |       | D3 <sub>hot</sub> to D0 because of a power state command does not perform an internal reset.    |  |  |  |

| 02    | RO   | 0b    | Reserved by PCI-SIG                                                                             |  |  |  |

|       |      |       | Power State (PS): This field is used both to determine the current power state of the           |  |  |  |

|       |      |       | controller and to set a new power state. The values are:                                        |  |  |  |

| 04.00 | DW   | 004   | 00b – D0 state                                                                                  |  |  |  |

| 01:00 | RW   | 00b   | 01b – D1 state                                                                                  |  |  |  |

|       |      |       | 10b – D1 state                                                                                  |  |  |  |

|       |      |       | 11b – D2 state<br>11b – D3нот state                                                             |  |  |  |

Figure 33: Offset PMCAP + 4h: PMCS - PCI Power Management Control and Status

| Bits | Type | Reset | Description                                                                                                                                                                   |

|------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      |       | When in the D3 <sub>HOT</sub> state, the controller's configuration space is available, but the register I/O and memory spaces are not. Additionally, interrupts are blocked. |

### 3.8.3 Message Signaled Interrupt Capability (Optional)

Figure 34: Message Signaled Interrupt Capability (Optional)

| Start      | End        | Symbol | Name                                               |

|------------|------------|--------|----------------------------------------------------|

| MSICAP     | MSICAP+1h  | MID    | Message Signaled Interrupt Capability ID           |

| MSICAP+2h  | MSICAP+3h  | MC     | Message Signaled Interrupt Message Control         |

| MSICAP+4h  | MSICAP+7h  | MA     | Message Signaled Interrupt Message Address         |

| MSICAP+8h  | MSICAP+Bh  | MUA    | Message Signaled Interrupt Upper Address           |

| MSICAP+Ch  | MSICAP+Dh  | MD     | Message Signaled Interrupt Message Data            |